东芝3D芯片堆叠策略:像建楼一样造闪存

东芝正在打造高层闪存和ReRAM芯片,预计原型样本将于明年推出。

高层或3D芯片的想法是:我们可以回避闪存或内存芯片存储密度增加的局限性,将它们向上堆叠,从而增加存储密度,就像高层住宅能够居住更多人一样。

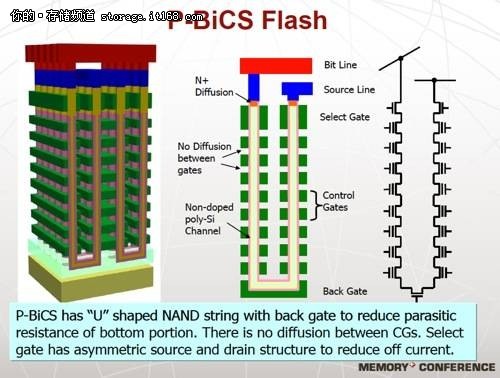

从Nikkei Electronics得知,东芝正在使用一种NAND、其p-BiCS技术以及ReRAM(阻性RAM)来构建3D堆叠,ReRAM是NAND潜在的替代技术,它结合了RAM和NAND的属性来提供字节寻址能力、DRAM级速度和NAND非易失性。

正如下图所示,3D闪存包含NAND堆叠层,它们通过通信孔(TSV或者Through Silicon Via)的来链接到堆栈基的堆栈控制器。这并不是将NAND芯片堆叠在另一个芯片之上,而是在单个芯片中堆叠NAND层。

东芝3D芯片堆叠策略:像建楼一样造闪存

东芝3D芯片堆叠策略:像建楼一样造闪存

东芝p-BiCS技术

东芝的p-BiCS NAND有一个50纳米大小的洞和16层,东芝的首席工程师Masaki Momodomi表示,当使用超过15层时,假设是类似的容量水平的话,p-BiCS要比普通的NAND更便宜。该公司计划在明年提供128Gbit和256Gbit原型样本,在2014年提供工程样本,在2015年进行量产,我们还需要等待两年才能在市面上看到这个产品。

ReRAM技术也是类似的时间表。它比NAND有更快的写入时间,东芝认为ReRAM能够发挥与p-BiCS不同的作用,它将用于比p-BiCS更接近CPU的未知,STT-RAM用于SSD中的高速缓存。Objective Analysis的Jim Handy表示:“ReRAM将被用于高性能应用程序,它们的写入速度快于NAND,它们是随机访问设备,而NAND不是,它们不需要ECC,这些都能够带来更快性能。”

东芝的ReRAM技术的原型样本、工程样本和量产时间将于p-BiCS基本一致。东芝展示了64Gbit ReRAM设备的图片,但东芝计划提供相当容量的p-BiCS和ReRAM。

东芝计划减小现有1Xnm(19纳米)NAND单元的大小,将于今年推出1Ynm(据我们了解18-14纳米),明年推出1Znm(10-13纳米)产品。

Handy表示:“所有这些新技术(MRAM、ReRAM、FRAM等)都比NAND有更好的表现(BiCS是NAND的一种),但更加昂贵。对于内存而言,成本就是一切,这些替代品在这方面并没有做好。这些技术的承诺是它们能够跨越过去NAND的扩展限制,如果真的是这样的话,它们最终将比NAND更便宜。”

“东芝谈到1y和1z,19纳米后的工艺。我怀疑NAND大约会在10纳米停止扩展,但BiCS将导致NAND价格继续下降。”

我们会继续看到NAND尺寸下降吗?还是通过3D从NAND的堆叠中获得更多容量?Handy表示:“最新的ITRS(国际半导体技术发展路线图)为NAND指出了两个不同的方向,垂直(BiCS)和传统。行业真的不知道未来将如何发展,但让我们拭目以待。”

本文来源于网络,如有侵权,请联系我删除。